超大规模集成电路设计中的MOS器件原理及其设计实践

超大规模集成电路(VLSI)的设计是现代信息技术的基石,其核心在于对成千上万个微型元器件的精确设计与集成。在众多半导体器件中,金属-氧化物-半导体场效应晶体管(MOSFET,简称MOS器件)因其低功耗、高集成度和良好的可扩展性,成为了VLSI设计的绝对主流。理解MOS器件的工作原理,是进行高效、可靠集成电路设计的前提。

一、MOS器件的基本结构与工作原理

MOS器件本质上是一个电压控制的开关。其基本结构由源极(Source)、漏极(Drain)、栅极(Gate)和衬底(Body)构成。栅极与沟道之间由一层极薄的绝缘氧化物(如二氧化硅)隔开,形成所谓的“MOS”结构。

核心工作原理:当在栅极施加电压(VGS)时,会在栅极下方的半导体衬底表面感应出电荷,形成导电沟道(对于N-MOS,感应出电子;对于P-MOS,感应出空穴)。一旦沟道形成,源极和漏极之间便可通过电流(IDS),其大小受栅极电压和漏源电压(VDS)共同控制。当栅极电压低于阈值电压(Vth)时,沟道无法形成,器件处于关闭(截止)状态,电流极小。这一“开”与“关”的状态,直接对应数字电路中的逻辑“1”和“0”。

二、MOS器件特性对VLSI设计的影响

- 阈值电压(Vth):是器件开启的“门槛”。设计时必须精确控制,因为它直接影响电路的开关速度、功耗和噪声容限。工艺波动导致的Vth变化是设计时需要重点考虑的公差因素。

- 跨导(g_m):表征栅极电压控制沟道电流的能力。高跨导意味着用较小的电压变化就能产生较大的电流变化,这对模拟电路(如放大器)的增益和数字电路的开关速度至关重要。

- 沟道长度调制效应:在饱和区,漏极电流会随V_DS微小增加而略微上升,这等效于输出电阻有限。该效应会影响模拟电路的增益精度和电流源的理想程度。

- 亚阈值导通:当VGS略低于Vth时,仍有微弱的电流。在深亚微米工艺中,这一效应显著,是静态功耗的主要来源之一,在低功耗设计中必须严加管控。

- 寄生参数:包括栅源/栅漏覆盖电容、结电容、连线电阻等。在GHz级别的高频电路中,这些寄生效应会严重限制电路的最高工作速度,并引起信号完整性问题。

三、从器件原理到集成电路设计实践

VLSI设计是一个从器件物理向上构建复杂系统的过程。

- 数字电路设计:基于MOS器件的开关特性。设计核心是构建反相器(CMOS结构由互补的N-MOS和P-MOS组成),并以此为基础组合成各类逻辑门、触发器、存储器单元等。设计时需在速度(器件尺寸、驱动能力)、功耗(静态功耗、动态功耗)和面积之间进行精妙的权衡。例如,采用多阈值电压库、电源门控等技术来优化功耗。

- 模拟/混合信号电路设计:更直接地利用MOS器件的电流-电压特性。例如,利用饱和区MOS管平方律特性设计差分放大器,利用深线性区的MOS管作为压控电阻。设计高度依赖于器件的匹配性、噪声特性(如1/f噪声)和线性度,对工艺偏差极其敏感。

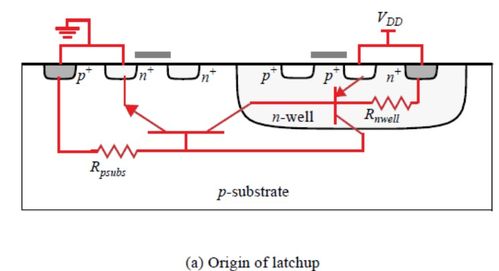

- 物理设计与可靠性:

- 尺寸缩放:遵循摩尔定律,器件尺寸不断缩小(纳米级),带来了短沟道效应、量子隧穿、热载流子效应等一系列挑战,迫使设计方法不断革新(如FinFET等三维结构器件的采用)。

- 功耗与热管理:单位面积功耗密度激增,热效应成为限制性能与可靠性的关键。需要在架构、电路和物理布局层面进行协同优化。

- 信号完整性:在超大规模集成下,互连线延迟已超过门延迟成为主要矛盾。时钟偏移、电源网络噪声(IR Drop)、串扰等问题必须通过精心的版图规划和签核分析来解决。

###

MOS器件原理是通往超大规模集成电路设计殿堂的钥匙。从理解一个晶体管的基本电流方程开始,到设计包含数十亿晶体管的复杂片上系统(SoC),其间贯穿着对器件物理特性的深刻把握与巧妙运用。随着工艺节点进入深纳米乃至埃米时代,新的器件物理(如隧穿晶体管、自旋器件)也在探索中,但MOS器件的基本原理及其所奠定的设计思想,仍将在未来很长一段时间内,持续引领着集成电路技术的创新与发展。

如若转载,请注明出处:http://www.6shuju.com/product/31.html

更新时间:2026-03-03 13:31:06