集成电路版图设计软件开发

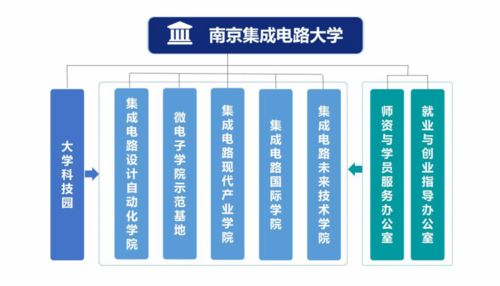

集成电路(IC)版图设计软件是现代电子设计自动化的核心工具,用于将电路设计图转换为可供制造的物理版图。该软件开发涉及多学科交叉,包括计算机科学、电子工程和材料科学等,其发展水平直接影响着芯片设计的效率与质量。

一、软件功能模块

集成电路版图设计软件通常包含以下核心模块:

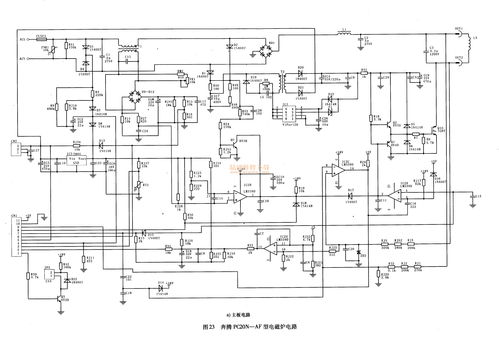

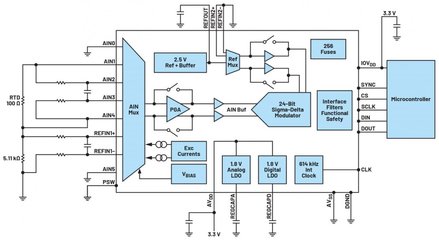

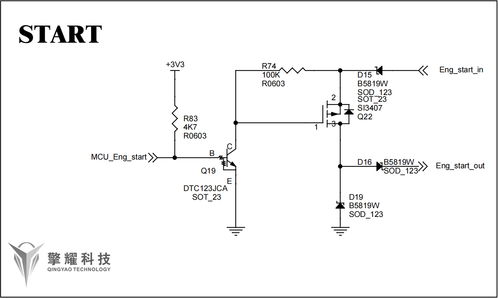

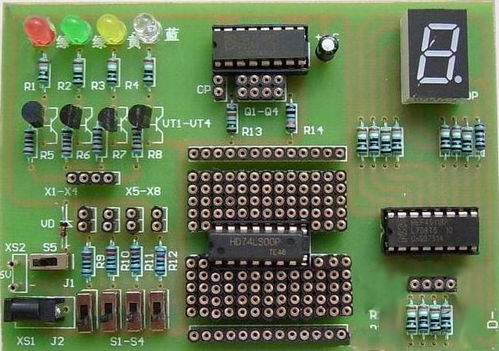

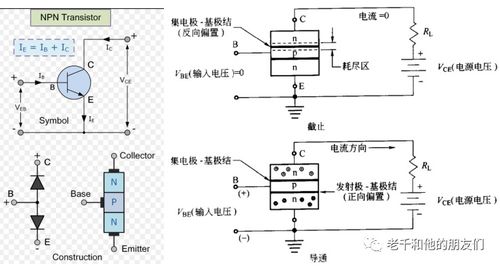

- 原理图输入与仿真:支持电路图的绘制与功能验证,确保逻辑正确性。

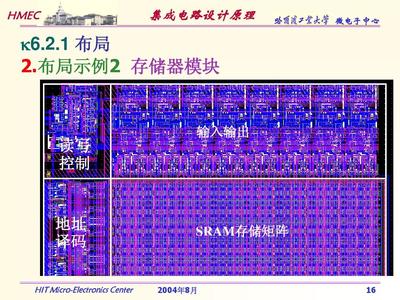

- 版图编辑:提供图形界面,允许工程师绘制晶体管、电阻、电容等元件的物理布局。

- 设计规则检查:自动检测版图是否符合制造工艺的物理限制,如最小线宽、间距等。

- 版图与原理图对比:确保物理版图与原始电路设计一致。

- 参数提取与后仿真:从版图中提取寄生参数,并进行精确的性能仿真。

二、开发挑战与趋势

- 工艺节点缩小:随着芯片制程进入纳米级,软件需处理更复杂的设计规则和寄生效应。

- 自动化与AI辅助:机器学习技术被用于优化布局布线,减少人工干预。

- 云平台集成:基于云端的协作设计环境,支持多团队远程并行开发。

- 安全性需求:保护知识产权,防止设计数据泄露。

三、主流软件工具

目前市场上主流的IC版图设计软件包括:

- Cadence Virtuoso:行业标准工具,提供全面的定制化设计流程。

- Synopsys Custom Compiler:基于云平台,强调易用性与自动化。

- Mentor Graphics(现为Siemens EDA):专注于验证与制造接口。

四、未来展望

随着物联网、人工智能和5G技术的快速发展,集成电路版图设计软件将更注重智能优化、多物理场仿真和异构集成支持。开源工具(如Google的SkyWater PDK)的兴起,也为中小设计团队降低了入门门槛。

集成电路版图设计软件的开发是推动半导体产业进步的关键,其创新将继续赋能更高效、更可靠的芯片制造。

如若转载,请注明出处:http://www.6shuju.com/product/21.html

更新时间:2026-03-03 03:24:04